# D3.3 REWIRE Design Time Secure Operational Framework - Final Version

Project number: 101070627

Project acronym: REWIRE

Project title: REWiring the Compositional Security VeRification and Assur-

ancE of Systems of Systems Lifecycle

Project Start Date: 1st October, 2022

**Duration:** 36 months

Programme: HORIZON-CL3-2021-CS-01

**Deliverable Type:** Report

Reference Number: HORIZON-CL3-2021-CS-01-101070627/ D3.3 / v1.0

Workpackage: WP2

Actual Submission Date: 30th September, 2025

Responsible Organisation: SECURA

Editor: Sjors Van den Elzen

Dissemination Level: Public

Revision: v1.0

Abstract:

D3.3 presents the final versions of the components participating in the design-time phase of the REWIRE framework and the definition of the trust boundary of the system. Design and implementation details were presented for the Secure SW Update, the Compositional Verification and Validation component, the SW/FW Vulnerability Analysis, the AADL-based traceability of requirements, the MSPL-based Security Policies, the Risk Assessment, and the establishment of authenticated channels. Benchmarking results were provided, demonstrating the performance of the implemented solutions.

**Keywords:**

Compositional Verification, Vulnerability Analysis, Risk Assessment, Software Update, Security Policies

The The project REWIRE has received funding from the European Union's Horizon Europe research and innovation programme under grant agreement No 101070627.

#### **Editor**

Sjors Van den Elzen(SECURA)

#### Contributors (ordered according to beneficiary numbers)

Stylianos Basagiannis, Simone Fulvio Rollini (UTRCI)

Dimitris Karras, Nikos Fotos, Stefanos Vasileiadis, Thanassis Giannetsos (UBITECH)

Corentin Verhamme, Francois Koeune (UCL)

Sjors Van den Elzen (SECURA)

Samira Briongos, Javier de Vicente Gutierez (NEC)

Jesus Sanchez (ODINS)

Paraskevas Papanikolaou, Charoula Pechilvani, Athanasios Athanasiadis (KENOTOM)

Ilias Aliferis (UNIS)

#### **Disclaimer**

The information in this document is provided "as is", and no guarantee or warranty is given that the information is fit for any particular purpose. The content of this document reflects only the author's view – the European Commission is not responsible for any use that may be made of the information it contains. The users use the information at their sole risk and liability. This document has gone through the consortium's internal review process and is still subject to the review of the European Commission. Updates to the content may be made at a later stage.

REWIRE D3.3 Page I

# **Executive Summary**

One of the core offerings of REWIRE is the secure lifecycle management of embedded systems considering the trend towards the increasing adoption of OpenHW architectures, such as RISC-V, through the provision of the necessary security and trust enablers. In this regard, REWIRE aims to address the key challenge of ensuring the correctness of software and hardware artefacts for achieving a high level of trustworthiness guarantees in embedded systems, through a holistic security framework, whose architectural details were presented in D2.2. This framework comprises two core phases, the **Design-time** and **Runtime** phases, which aim to cover the entire operational lifecycle of the device. The present deliverable is dedicated to the detailed documentation of the **artefacts**, **schemes**, and **methods participating** in the design-time phase of the framework and their role towards the achievement of the goal of this phase, namely the definition of the trust boundary of the system, i.e., the identification of device properties that can be formally verified during design-time and those that need to be verified dynamically during runtime.

One of the core outcomes of the design-time phase is the deployment of mitigation measures against the identified threats and vulnerabilities of the devices through the appropriate *security and operational policies*. One such measure is the deployment and installation of software updates in order to mitigate such vulnerabilities. In this context of REWIRE, this is performed through the **Secure SW Update with Authenticated Encryption (AE)**, which is analysed in Chapter 2. As REWIRE aims to ensure the installation of such updates in a manner that fulfils the overarching security requirements of the target domain, AE is a symmetric cryptographic construction employed for securing the communication channel used for software updates. Note that REWIRE supports two modalities of the SW update process for ensuring applicability and scalability in multiple types of operational domains, namely "1-to-1" for the distribution of an update to a single device, and "1-to-many" for the distribution of an update from a single source to multiple recipients.

The backbone of the design-time phase of REWIRE is the Compositional Verification and Validation Component, which is described in detail in Chapter 3, and its core functionality entails the use of Formal Verification tools in order to verify all security protocols and schemes, before they are synthesized into the actual devices. In this deliverable, we expand on the rationale and motivation behind the use of Verifpal as the core Formal Verification tool of this component, as well as its implementation details in the context of REWIRE. Then, we focus on the Formal Verification of the Configuration Integrity Verification (CIV) scheme, which relies on local attestation using key restriction usage policies. Note that this is a key innovation of REWIRE, as the verification of such schemes has not yet been explored in the literature.

Chapter 4 is dedicated to the description of the **SW/FW Vulnerability Analysis** component of REWIRE, whose purpose is the analysis of the SW or FW image of a device, in order to identify any threats and vulnerabilities that need to be mitigated through the security enablers of REWIRE. This component employs a mixture of new and well-established fuzzing techniques, capable of coping with the internal interdependencies of RISC-V architectures, in order to *provide more information to the SW Service Provider that enables them to push the appropriate software update*. Then, the identified vulnerabilities are pushed to the **Risk Assessment** component, so that the appropriate security controls as mitigation measures are identified and pushed in the form of policies.

One core aspect of achieving the goal of REWIRE for enhancing the secure lifecycle managements of

REWIRE D3.3 Page II

devices is the ability to trace the achievement of the security requirements associated with the technical components of REWIRE, towards the achievement of the overarching requirements, security goals, and specifications of the use cases of REWIRE. This is achieved through the Architecture Analysis & Design Language (AADL)-based System Modelling methodology, which is employed by REWIRE in order to create a virtual representation of the assets comprising the domain infrastructure, their interconnectivity, and the associated asset properties or requirements. Then, the Resolute language is used for ratifying and validating the correctness and achievement of the aforementioned requirements through architectural assurance cases.

As aforementioned, a core outcome of the design-time phase is the identification of the device properties that need to be verified dynamically during runtime, based on the identified *trust boundary* of the device. In this regard, the **security controls** that need to be deployed for this verification is performed through the definition of **security policies**, dictating the actions (and details regarding their periodicity) that need to be performed. In the context of REWIRE, these policies are expressed using the **Medium Security Policy Language (MSPL)**, which has been identified as possessing the granularity and expressiveness requirements of REWIRE, and deployed through the **Policy Orchestrator** to the intended devices. Chapter 6 is dedicated to the provision of concrete examples of such MSPL-expressed policies in the context of the use cases, specifically the **Smart Cities**, **Automotive**, and **Smart Satellites** use cases.

The **REWIRE Risk Assessment Component**, described in Chapter 7, is a core aspect of REWIRE, whose purpose is to maintain an up-to-date **risk graph** of the entire domain ecosystem, based on the threats and vulnerabilities of the devices participating in the target domain infrastructure. One core target of the RA component is the calculation of the **Required Trust Level (RTL)** of the devices, referring to the baseline level of trust that needs to be achieved so that they can be considered trustworthy, based on the identified risks and available mitigation measures. Thus, the RA component can be used in order to guide the operation of a Trust Assessment methodology, which falls outside the scope of REWIRE, but REWIRE aims to provide all required tools and functionalities for guiding its operation.

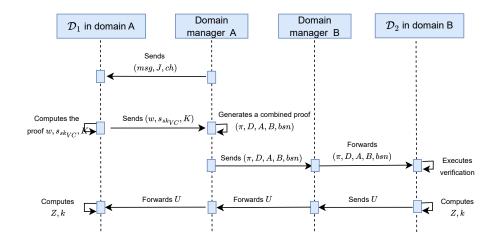

Finally, Chapter 8 is dedicated to the methodology employed by REWIRE in order to establish secure and authenticated communication channels for achieving all overarching security and privacy requirements, considering both communication within the same domain and communication between different domains. This is achieved through the use of the Anonymous Authenticated Credential Key Agreement (AACKA) scheme, based on which REWIRE designs a novel BBS-based AACKA protocol (considering that the credential used in the ZTO process is a BBS signature), resulting in the establishment of secure and anonymous communication channels.

REWIRE D3.3 Page III

# **Contents**

| 1 | Intro                                                                     | oduction 4                                                         |

|---|---------------------------------------------------------------------------|--------------------------------------------------------------------|

|   | 1.1                                                                       | Scope and Purpose                                                  |

|   | 1.2                                                                       | Relation to other WPs and Deliverables                             |

|   | 1.3                                                                       | Deliverable Structure                                              |

| _ | DEV                                                                       | VIDE Converting OW the data Decomposite Authorities and Engagement |

| 2 |                                                                           | VIRE Secure SW Update Process with Authenticated Encryption  8     |

|   | 2.1                                                                       | High-level Summary of the State-of-the-Art on Side-Channel Attacks |

|   | 2.2                                                                       | Design of a Masked Gadget Robust against Physical Defaults         |

|   |                                                                           | 2.2.1 The challenge of composability                               |

|   |                                                                           | 2.2.2 Challenge of Physical Defaults in Composable Gadgets         |

|   |                                                                           | 2.2.3 Solving the Issue even for Low-Latency                       |

|   | 0.0                                                                       | 2.2.4 Other potential Applications                                 |

|   | 2.3                                                                       | Application of the Masked Gadget to ASCON                          |

|   |                                                                           | 2.3.1 Mode-level security against leakage                          |

|   |                                                                           | 2.3.2 Implementations of the Ascon permutation                     |

|   |                                                                           | 2.3.3 CIML2+CCAmL2 with uniform masking                            |

|   |                                                                           | 2.3.4 CIML2+CCAmL1 with leveling                                   |

|   | 0.4                                                                       | 2.3.5 Performance evaluation                                       |

|   | 2.4                                                                       | Primitive-Level and Model-Level Countermeasures Evaluation         |

|   |                                                                           | 2.4.1 Experimental setup                                           |

|   |                                                                           | 2.4.2 Leakage-resilient PRF (STM32F4)                              |

|   | 0.5                                                                       | 2.4.3 Protected AES Core (STM32U5)                                 |

|   | 2.5                                                                       | Lessons Learned towards Sustainable Security                       |

|   |                                                                           | 2.5.1 The challenges in achieving physical security                |

|   |                                                                           | 2.5.2 Sustainable security for REWIRE                              |

| 3 | npositional Verification and Validation of REWIRE Attestation Protocol 41 |                                                                    |

|   | 3.1                                                                       | Tools and Languages                                                |

|   |                                                                           | 3.1.1 Security Properties                                          |

|   |                                                                           | 3.1.2 Threat Model                                                 |

|   | 3.2                                                                       | High-level Overview of the CIV Protocol                            |

|   | 3.3                                                                       | CIV Modeling and Verification Approach                             |

|   |                                                                           | 3.3.1 Modelling in Verifpal                                        |

|   |                                                                           | 3.3.2 Analysis Scenarios                                           |

|   |                                                                           | 3.3.3 Properties of Interest                                       |

|   | 3.4                                                                       | CIV Verification Results                                           |

|   |                                                                           | 3.4.1 Interpreting the Violation                                   |

| 4 | CM                                                                        | EW Vulnevehility Analysis                                          |

| 4 | <b>5W</b> /4.1                                                            | FW Vulnerability Analysis 54 The REWIRE Solution                   |

|   | 4.1                                                                       |                                                                    |

|   |                                                                           | 4.1.1 Analysis of RISC-V Architecture through Updating Qiling      |

|   |                                                                           | 4.1.2 Selection of Seeds for Construction of Fuzzing Campaign 61   |

REWIRE D3.3 Page IV

# D3.3 - REWIRE Design Time Secure Operational Framework - Final Version

| _   |            | <u>-</u>                                                                             |          |

|-----|------------|--------------------------------------------------------------------------------------|----------|

|     | 4.2        | REWIRE SW/FW Vulnerability Analysis Benchmarking                                     | 61       |

|     |            |                                                                                      | 63       |

|     |            |                                                                                      | 64<br>64 |

| 5   |            | delling and Requirements Traceability of Use Cases through AADL                      | 69       |

|     | 5.1<br>5.2 | Introduction                                                                         |          |

|     | 5.3        | Summary of Secure SW Update Security Properties                                      | 72       |

|     | 0.0        | 5.3.1 Security Properties and System Description                                     |          |

|     |            |                                                                                      |          |

|     |            | 5.3.3 System Model                                                                   |          |

|     |            | 9                                                                                    |          |

|     | 5.4        | ·                                                                                    |          |

|     |            |                                                                                      |          |

|     |            | 5.4.2 1-to-Many Scenario                                                             | 84       |

| 6   |            | antiation of REWIRE MSPL-based Security Policies                                     | 87       |

|     | 6.1        | REWIRE Policy Orchestration and Device Lifecycle Management                          |          |

|     | 6.2        | Security Policy Operational Codes                                                    |          |

|     |            | 6.2.2 Use Case 2: Adaptive In-Vehicle SW & FW Patch Management & Software Func-      |          |

|     |            | tions Migration                                                                      | 91       |

|     |            | Services                                                                             | 94       |

|     | 6.3        |                                                                                      |          |

| 7   |            | VIRE Continuous and Modular Risk Assessment                                          | 99       |

|     |            | Overview and Updates on Second Release                                               |          |

|     | 7.2<br>7.3 | Functional Specifications                                                            |          |

|     | 7.0        | 7.3.1 High-level Flow of Actions                                                     |          |

|     |            | 7.3.2 Component Analysis                                                             | 105      |

|     | 7.4        | 7.3.3 REWIRE Risk Assessment Framework                                               |          |

|     | 7.4<br>7.5 | Streamlining TARA with Automated Attack Path Calculation                             |          |

|     | 7.6        | Specification of Implemented Interfaces                                              |          |

|     | 7.7        | Reinforcing RTL Calculation by Abstracting the Underlying Risk Quantification Engine | 129      |

| 8   | Esta       |                                                                                      | 131      |

|     | 8.1        | Syntax and Security model for a AACKA protocol                                       |          |

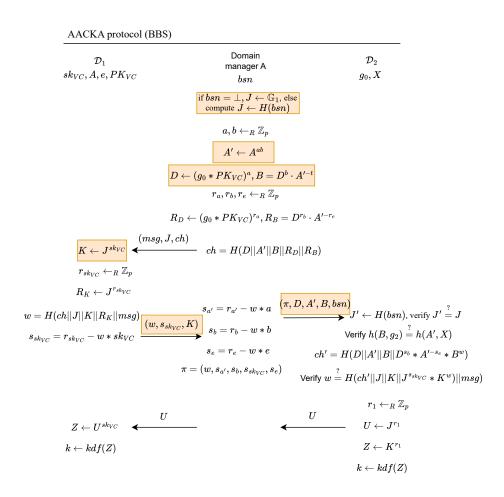

|     | 8.2<br>8.3 | The first BBS-based AACKA protocol with a single signer                              |          |

|     | 8.4        | The second AACKA protocol with two separate signers                                  |          |

|     | 8.5        | The running time for randomization of credential                                     |          |

| 9   | Con        | aclusions 1                                                                          | 144      |

| Bil | blioa      | raphy 1                                                                              | 146      |

REWIRE D3.3 Page V

# **List of Figures**

| 1.1        | Relation of D3.3 with other WPs and Deliverables                                                                                                                                              | 6   |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 2.1<br>2.2 | Iterative AND architecture                                                                                                                                                                    | 15  |

| ۷.۷        | design of Figure 2.1 instantiated with HPC3 gadgets. Middle: same design instantiated                                                                                                         |     |

| 2.3        | with HPC4 gadgets. Right: same as left, but keeping $s=0$                                                                                                                                     | 15  |

| 2.0        | protected against DPA, the green ones have to be protected against SPA and the white ones do not require protection against side-channel leakage.                                             | 19  |

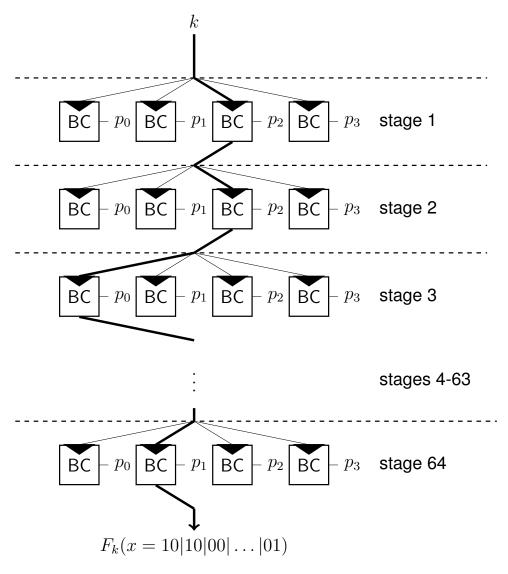

| 2.4        | Masked Ascon primitive implementation: $p_c$ denotes the round constant addition, $p_s$ de-                                                                                                   | 10  |

|            | notes the substitution layer that is split between the operations prior to the AND gate and the operations that use its output. For the operands that are not used in the AND gate, it        |     |

|            | require a synchronization register. The linear layer $p_l$ is applied over the state and $p(S_{in})$ designates a round of the Ascon permutation made over the state $S_{in}$                 | 21  |

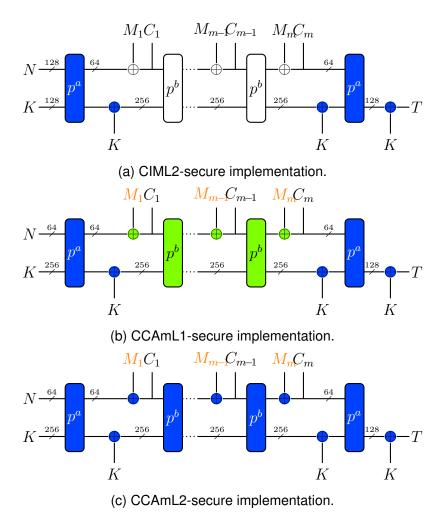

| 2.5        | Uniformly protected implementation ensuring CIML2 and CCAmL2                                                                                                                                  |     |

| 2.6        | Leveled implementation ensuring CIML2 and CCAmL1                                                                                                                                              |     |

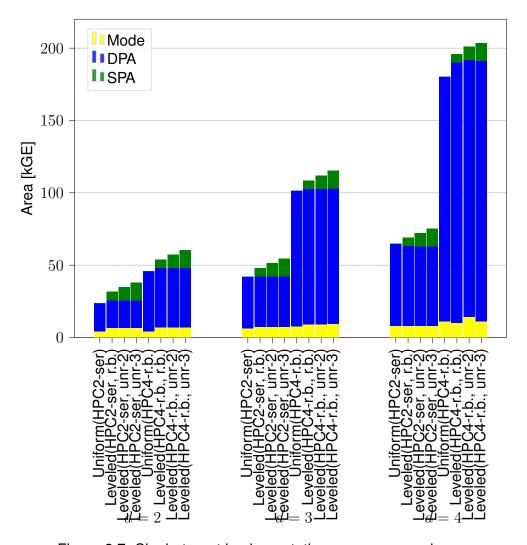

| 2.7        | Single-target implementations: area comparisons.                                                                                                                                              |     |

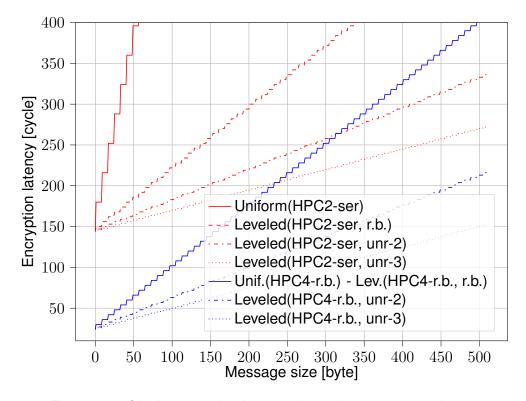

| 2.8        | Single-target implementations: latency comparisons.                                                                                                                                           |     |

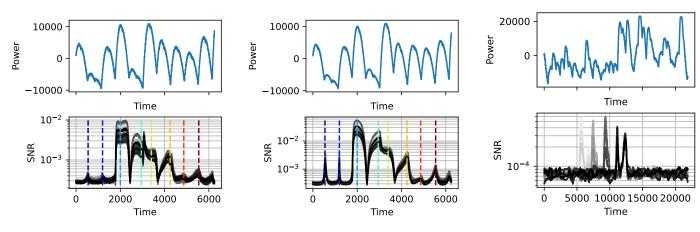

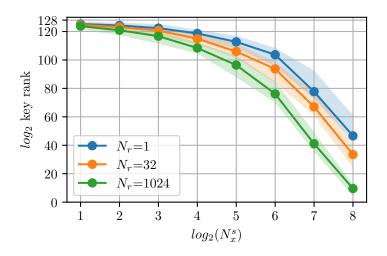

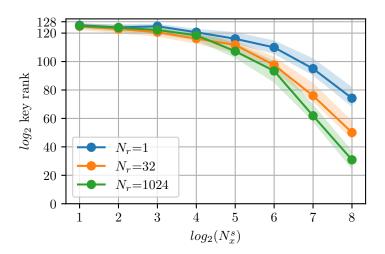

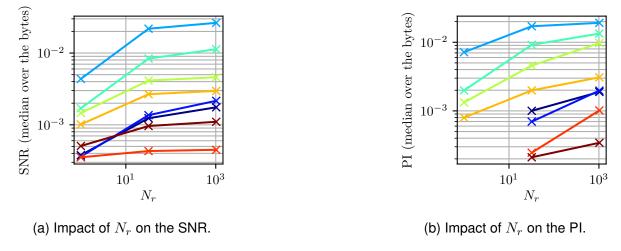

| 2.9        | Comparison of the SNR for both targets and impact of the repetition factor $N_r$ . The 16                                                                                                     |     |

|            | SNR curves with different shades of gray correspond to different S-boxes                                                                                                                      | 28  |

|            | Leakage-resilient PRF, $N_x^s = 4$ ( $n_x = 2$ )                                                                                                                                              | 29  |

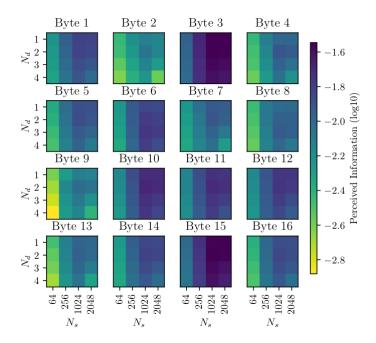

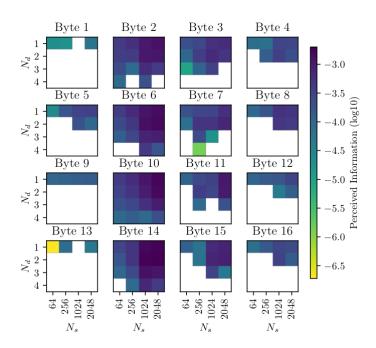

| 2.11       | PI of the STM32F4 target for all the bytes and the whole parameter space with $N_r=1$ ,                                                                                                       |     |

|            | displayed in log scale. As X-axis we display the number of selected Points-of-Interest $(N_s)$                                                                                                |     |

|            | and as Y-axis the number of output dimensions ( $N_d$ ) for the LDA. The PI is computed for                                                                                                   | 0.4 |

| 0 10       | one million traces corresponding to different plaintexts/keys                                                                                                                                 | 31  |

| 2.12       | PI of the STM32F4 target for all the bytes and the whole parameter space with $N_r = 1024$ , displayed in log scale. As X-axis we display the number of selected Points-of-Interest ( $N_s$ ) |     |

|            | and as Y-axis the number of output dimensions ( $N_d$ ) for the LDA. The PI is computed for                                                                                                   |     |

|            | one million traces corresponding to different plaintexts/keys                                                                                                                                 | 32  |

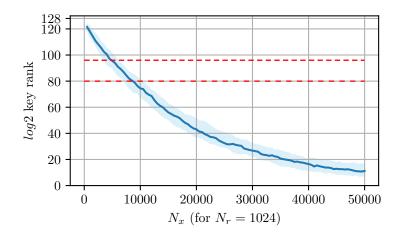

| 2.13       | Median and quartiles of the log key rank estimated on the training set for the unprotected                                                                                                    | 02  |

|            | AES coprocessor of the STM32F4 (estimated from 100 independent attacks)                                                                                                                       | 33  |

| 2.14       | Median and quartiles of the log key rank estimated on the test set for the unprotected AES                                                                                                    |     |

|            | coprocessor of the STM32F4 (estimated from 100 independent attacks)                                                                                                                           | 33  |

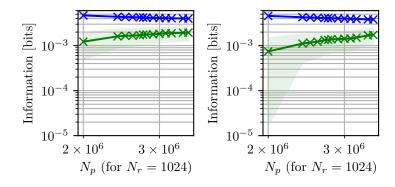

| 2.15       | PI (green) and TI (blue) for the most informative bytes on the STM32F4                                                                                                                        | 34  |

| 2.16       | Saturation of the median SNR (resp., PI) metrics when increasing $N_r$ , for relevant POIs                                                                                                    |     |

|            | (resp., sets of POIs) of the STM32F4. Colors are the same as in Figure 2.9.                                                                                                                   | 34  |

| 2.17       | Median and quartiles of the log key rank estimated on the attack set for the unprotected                                                                                                      |     |

|            | AES coprocessor of the STM32F4 (estimated from 100 independent attacks)                                                                                                                       | 35  |

REWIRE D3.3 Page VI

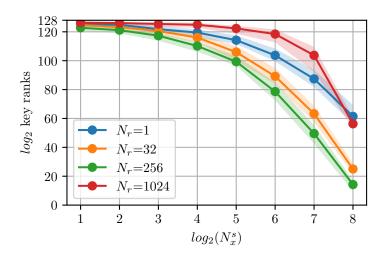

| 2.19                                                        | Median and quartiles of the key ranks for 100 independent attacks on the STM32U5 target (attack dataset computed after the interleaved training/test sets). Red horizontal lines correspond to target security levels / key ranks of $2^{80}$ and $2^{96}$                                                                                                                                                                                                                                                                                                                                                                                                                                        | 36<br>36<br>37                                           |

|-------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.8<br>3.9 | Symmetric Sealing Keys  Additional Enc-Dec Step in VPE to Key Manager Communication  Trace Leakage by the Tracer  Creation of s1 by the Tracer  Simplified Protocol Encoding  Counterexample to s1 Authenticity  Simplified Protocol Encoding Revised                                                                                                                                                                                                                                                                                                                                                                                                                                             | 51                                                       |

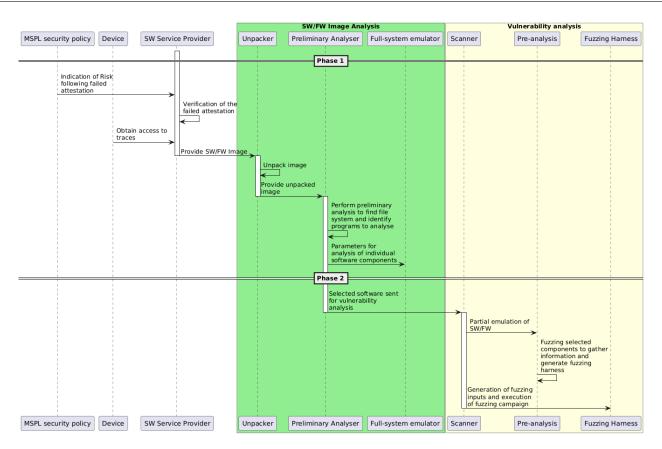

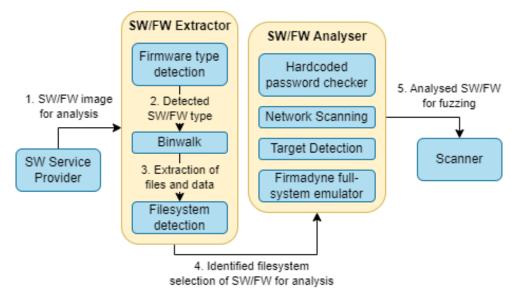

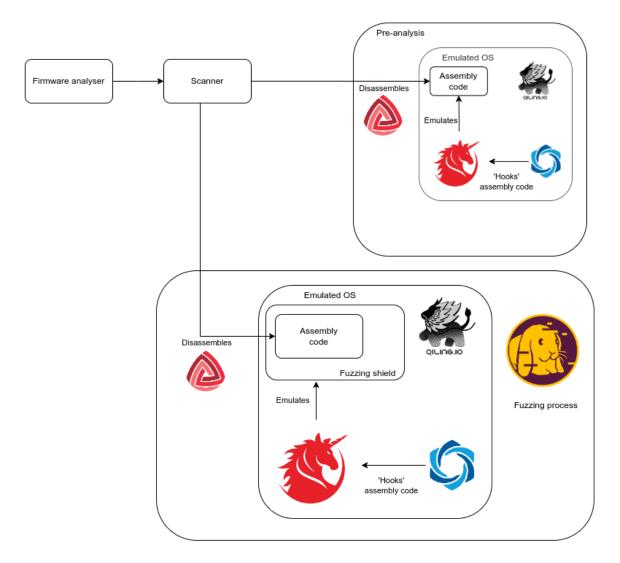

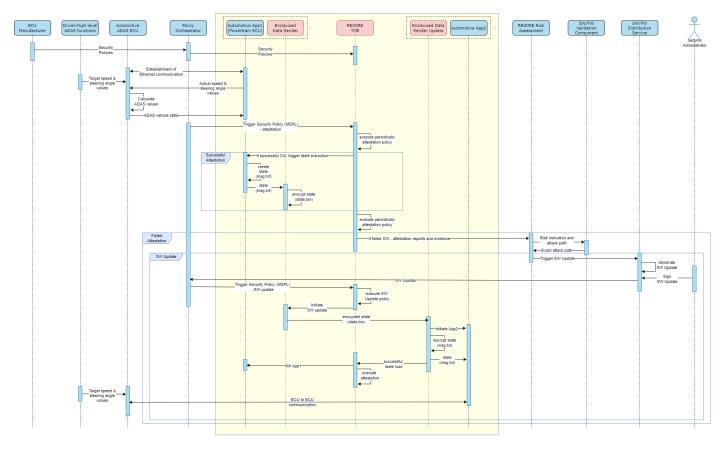

| 4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7               | The preliminary analysis of the SW/FW vulnerability analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 56<br>58<br>59<br>64<br>65<br>66                         |

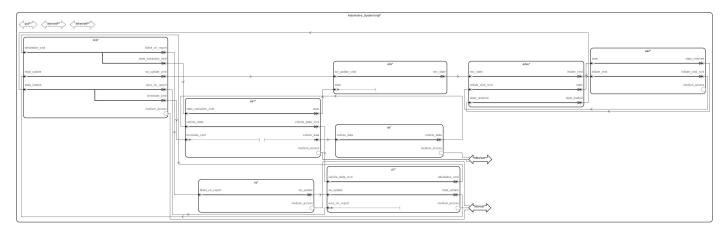

| 5.11<br>5.12<br>5.13                                        | Automotive Use Case AADL Diagram Automotive Use Case AADL Model Automotive Use Case Assurance Case Main Goal Automotive Use Case Assurance Case Evidence Linkage Automotive Use Case Assurance Case Evidence Linkage Automotive Use Case Assurance Case Claims Automotive Use Case Assurance Case Analysis Results Smart Cities Use Case Assurance Diagram Smart Cities Use Case AADL Diagram: 1-to-1 Smart Cities Use Case Assurance Case Main Goal: 1-to-1 Smart Cities Use Case Assurance Case Analysis Results: 1-to-1 Smart Cities Use Case AADL Model: 1-to-many Smart Cities Use Case Assurance Case Main Goal: 1-to-many Smart Cities Use Case Assurance Case Analysis Results: 1-to-many | 79<br>79<br>79<br>80<br>80<br>82<br>83<br>84<br>86<br>86 |

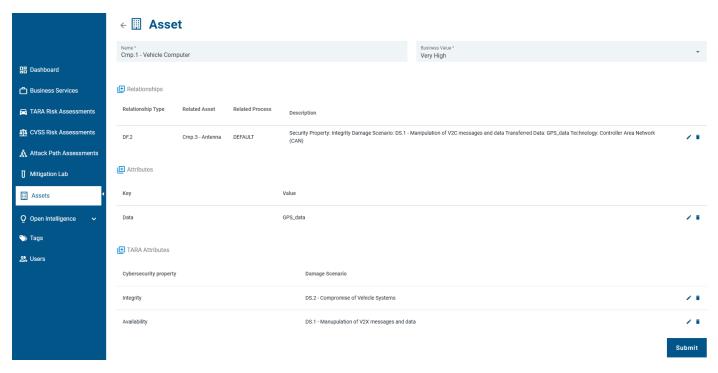

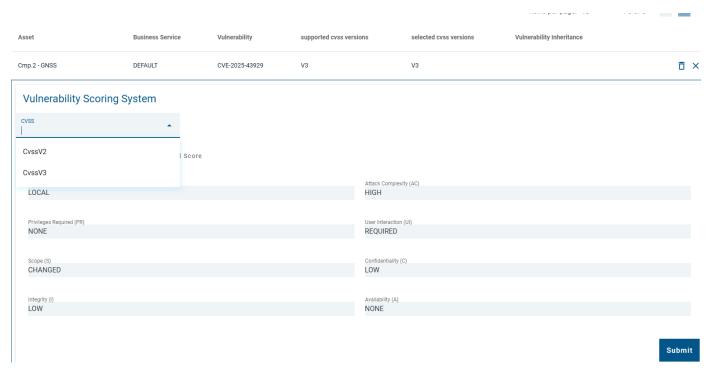

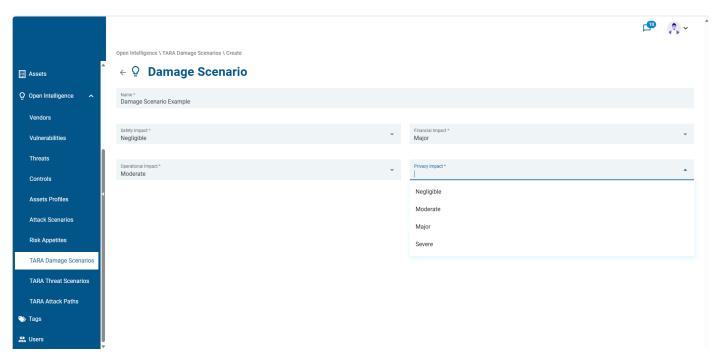

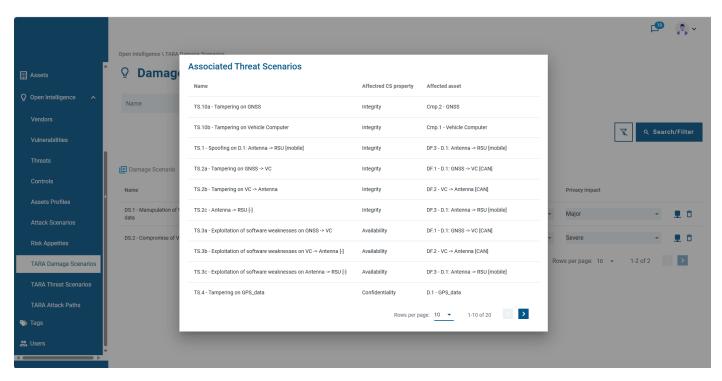

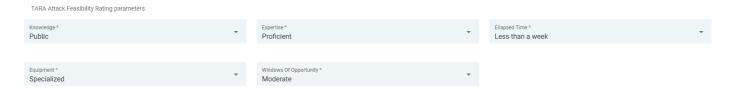

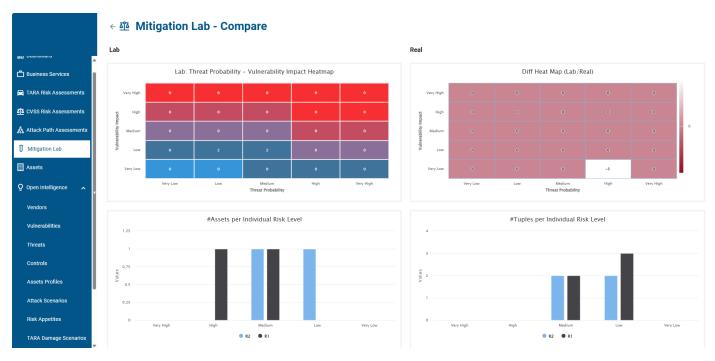

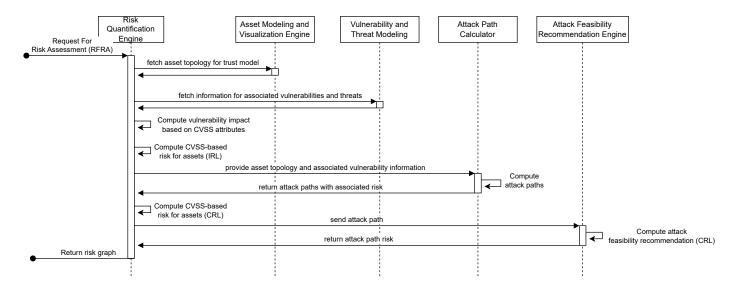

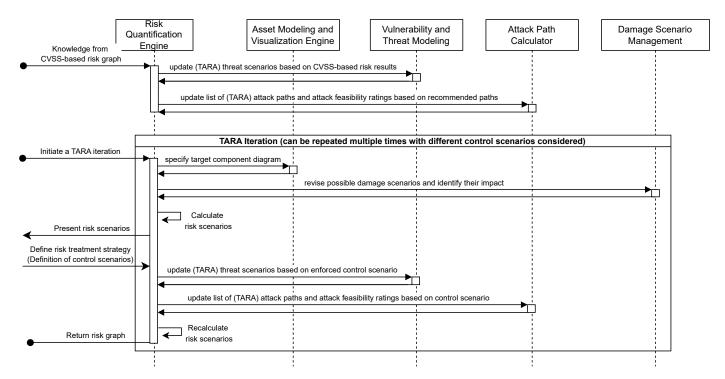

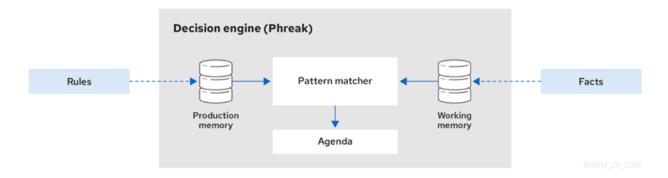

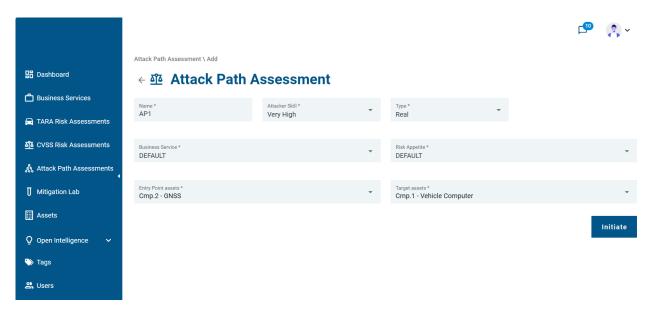

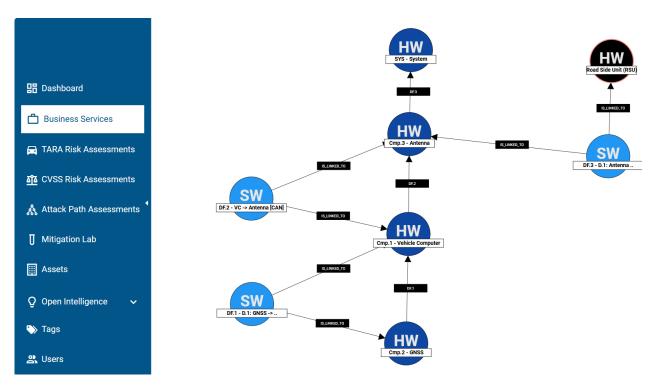

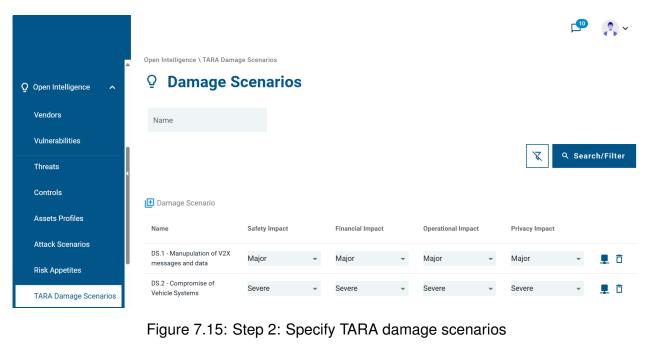

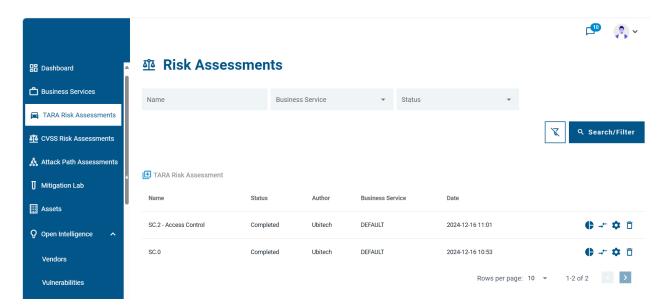

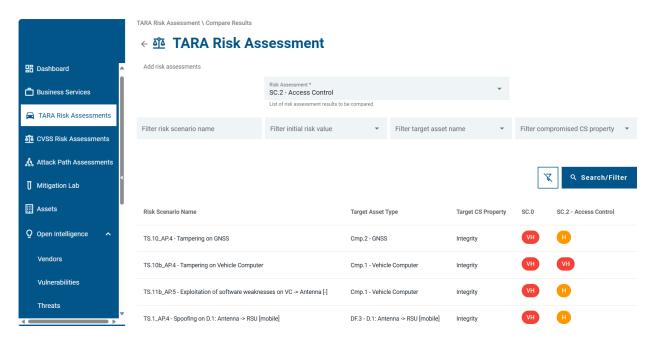

| 7.1<br>7.2<br>7.3<br>7.4<br>7.5<br>7.6<br>7.7               | Positioning of Risk Assessment within REWIRE architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 104<br>106<br>107<br>108                                 |

REWIRE D3.3 Page VII

# D3.3 - REWIRE Design Time Secure Operational Framework - Final Version

| 7.8  | Impact of applying a security control (e.g., software patch applied in the in-vehicle com-           |     |

|------|------------------------------------------------------------------------------------------------------|-----|

|      | puter) in the number of risk scenarios considered.                                                   |     |

| 7.9  | CVSS-based methodology with IRL and CRL calculations                                                 | 111 |

| 7.10 | TARA iterative process encompassing the enforcement of control scenarios in the risk                 |     |

|      | quantification process                                                                               | 112 |

| 7.11 | The Drools Engine internal architecture                                                              | 113 |

|      | Initializing a new Attack Path Assessment                                                            |     |

|      | Visualizing results of Attack Path Assessment                                                        |     |

|      | Step 1: Specify target component diagram                                                             |     |

|      | Step 2: Specify TARA damage scenarios                                                                |     |

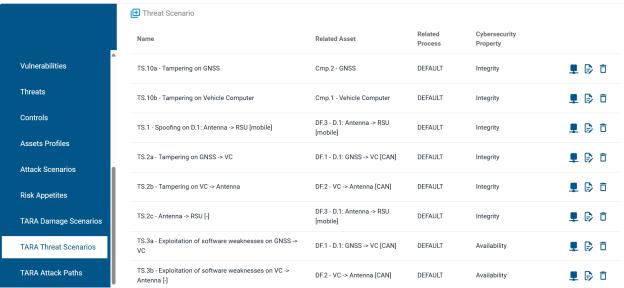

| 7.16 | Step 3: Specify TARA threat scenarios                                                                | 118 |

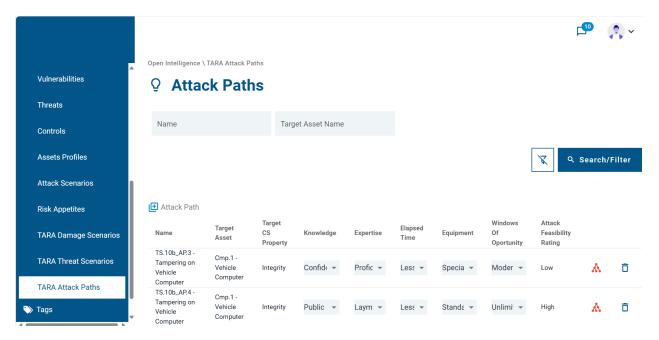

| 7.17 | Step 4: Specify TARA attack paths                                                                    | 119 |

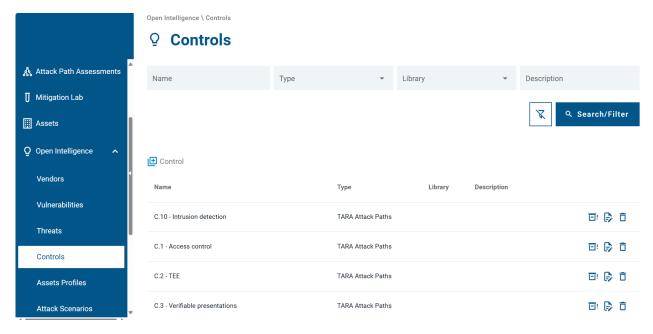

| 7.18 | Step 5: Specify TARA security controls                                                               | 123 |

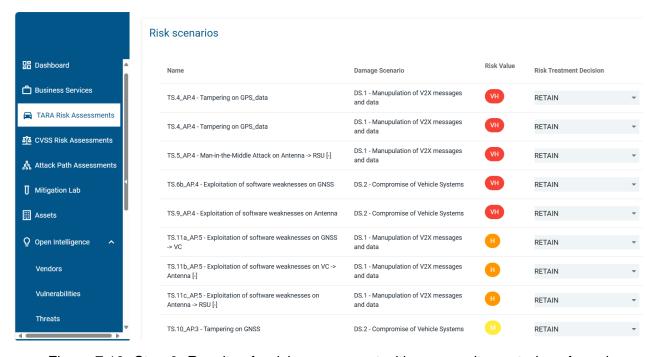

| 7.19 | Step 6: Results of a risk assessment with no security controls enforced                              | 123 |

| 7.20 | Step 7: List of risk assessment tasks: One with no controls applied and one with a single            |     |

|      | security control (Access control mechanisms enforced)                                                | 130 |

| 7.21 | Step 8: Comparison of results from different risk assessment tasks per risk scenario                 | 130 |

| 8.1  | The BBS-based AACKA protocol with a single signer                                                    | 134 |

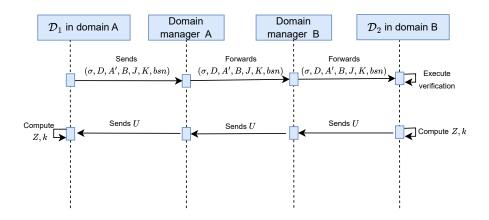

| 8.2  | Workflow of the AACKA protocol with a single signer in REWIRE                                        |     |

| 8.3  | The BBS-based AACKA protocol with two signers                                                        |     |

|      | Workflow of the AACKA protocol with two signers in REWIRE                                            |     |

| J.T  | **OHAHOV OF THE TATOLAR DISTOURS WITH TWO SIGNORS HERE *** ILL ** ** ** ** ** ** ** ** ** ** ** ** * | 174 |

REWIRE D3.3 Page VIII

# **List of Tables**

| 2.1  | Performance characteristic for low-latency uniformly implementations of Ascon, SHA3-512 and Ketje Sr using HPC4 gadgets: area in [kGE] and latency results for 1, 4 and 10 blocks |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.2  | of 576 bits (the specified block size of SHA-512)                                                                                                                                 |

| 2.2  | Cell Library obtained with Cadence Design Vision design toolchain                                                                                                                 |

| 2.3  | Comparison between the state of the art and our proposed solutions                                                                                                                |

| 2.4  | Comparison of the two approaches for protected implementations                                                                                                                    |

| 3.1  | CIV operations and corresponding Verifpal primitives                                                                                                                              |

| 3.2  | Passive Scenario Results                                                                                                                                                          |

| 3.3  | Passive Scenario With Leakage Results                                                                                                                                             |

| 3.4  | Active Scenario Results                                                                                                                                                           |

| 4.1  | Unit Test UT_FWSW_1 for FW/SW Validation                                                                                                                                          |

| 4.2  | Unit Test UT_FWSW_2 for FW/SW Validation                                                                                                                                          |

| 4.3  | Unit Test UT_FWSW_3 for FW/SW Validation                                                                                                                                          |

| 4.4  | Unit Test UT_FWSW_4 for FW/SW Validation                                                                                                                                          |

| 7.1  | Functional Specifications of REWIRE Risk Assessment                                                                                                                               |

| 7.2  | Rules for obtaining attack chains, expressed in DRL format                                                                                                                        |

| 7.3  | Add a process in REWIRE RA                                                                                                                                                        |

|      | Add an asset in REWIRE RA                                                                                                                                                         |

|      | Add a vulnerability in REWIRE RA                                                                                                                                                  |

| 7.7  | Add a control in REWIRE RA                                                                                                                                                        |

|      | Add a TARA Damage Scenario in REWIRE RA                                                                                                                                           |

| 7.9  | Add a TARA Attack Path in REWIRE RA                                                                                                                                               |

|      | Add a TARA Threat Scenario in REWIRE RA                                                                                                                                           |

|      | Add a Risk Assessment task in REWIRE RA                                                                                                                                           |

|      | Update TARA Attack Path in a Risk Assessment task in REWIRE RA                                                                                                                    |

|      | Update TARA Damage Scenario in a Risk Assessment task in REWIRE RA 126                                                                                                            |

| 7.14 | Update control in a Risk Assessment task in REWIRE RA                                                                                                                             |

|      | Execute a Risk Assessment in REWIRE RA                                                                                                                                            |

|      | Get Risk Assessment results in REWIRE RA                                                                                                                                          |

|      | Compare Risk Assessment results in REWIRE RA on a risk-scenario level                                                                                                             |

|      | Execute an Attack Path Calculator task in REWIRE RA                                                                                                                               |

| 7.19 | Get Attack Path Assessment results in REWIRE RA                                                                                                                                   |

| 8.1  | Comparisons between the CL and BBS signatures                                                                                                                                     |

| 8.2  | Notations used in the AACKA protocol                                                                                                                                              |

| 8.3  | Notation used in BBS-based PACKA protocol                                                                                                                                         |

REWIRE D3.3 Page IX

# Versioning and contribution history

| Version | Date       | Summary of Changes                                                                                                                                                                                                                                                                                            | List of Contributors                                                                                                                             |  |

|---------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|--|

| v0.1    | 13.01.2025 | Table of Contents                                                                                                                                                                                                                                                                                             | Thanassis Giannetsos (UBITECH), Sjors<br>Van den Elzen (SECURA)                                                                                  |  |

| v0.15   | 26.03.2025 | Definition of security properties and threat model of<br>Compositional Verification and Validation component<br>(Chapter 3)                                                                                                                                                                                   | Stylianos Basagiannis, Simone Fulvio Rollini (UTRCI)                                                                                             |  |

| v0.2    | 11.04.2025 | Design of masked gadget and application to ASCON in REWIRE SW Update process with Authenticated Encryption (Chapter 2)                                                                                                                                                                                        | Corentin Verhamme, Francois Koeune (UCL)                                                                                                         |  |

| v0.25   | 23.04.2025 | Description of SW/FW Vulnerability Analysis component (Chapter 4)                                                                                                                                                                                                                                             | Sjors Van den Elzen (SECURA)                                                                                                                     |  |

| v0.3    | 29.04.2025 | Description of process for the establishment of an authenticated channel (Chapter 8)                                                                                                                                                                                                                          | Samira Briongos (NEC)                                                                                                                            |  |

| v0.35   | 08.05.2025 | Description of the second release of the Risk Assessment component and instantiation in automotive use case (Chapter 7)                                                                                                                                                                                       | Dimitris Karras, Nikos Fotos, Thanasis<br>Giannetsos (UBITECH)                                                                                   |  |

| v0.4    | 13.05.2025 | Description of the AADL-based modelling and requirements traceability (Chapter 5)                                                                                                                                                                                                                             | Stylianos Basagiannis, Simone Fulvio Rollini (UTRCI)                                                                                             |  |

| v0.45   | 21.05.2025 | Description of REWIRE policy orchestrator and device lifecycle management (Chapter 6)                                                                                                                                                                                                                         | Stylianos Basagiannis, Simone Fulvio Rollini (UTRCI), Dimitris Karras, Thanasis Giannetsos (UBITECH)                                             |  |

| v0.5    | 27.05.2025 | Performance evaluation of masked gadget and countermeasures (Chapter 2)                                                                                                                                                                                                                                       | Corentin Verhamme, Francois Koeune (UCL)                                                                                                         |  |

| v0.55   | 04.06.2025 | Modelling and requirements traceability for Automotive use case (Chapter 5)                                                                                                                                                                                                                                   | Stylianos Basagiannis, Simone Fulvio<br>Rollini (UTRCI), Paraskevas Papaniko-<br>laou, Charoula Pechilvani, Athanasios<br>Athanasiadis (KENOTOM) |  |

| v0.6    | 12.06.2025 | Modelling and requirements traceability for Smart Cities use case (Chapter 5)                                                                                                                                                                                                                                 | Stylianos Basagiannis, Simone Fulvio Rollini (UTRCI), Jesus Sanchez (ODINS)                                                                      |  |

| v0.65   | 20.06.2025 | Examples of MSPL policies in all use cases (Chapter 6)                                                                                                                                                                                                                                                        | Stylianos Basagiannis, Simone Fulvio Rollini (UTRCI), Dimitris Karras, Thanasis Giannetsos (UBITECH)                                             |  |

| v0.7    | 01.07.2025 | Benchmarking of SW/FW Vulnerability Analysis (Chapter 4)                                                                                                                                                                                                                                                      | , ,                                                                                                                                              |  |

| v0.75   | 09.07.2025 | Compositional Verification and Validation of CIV scheme (Chapter 3)                                                                                                                                                                                                                                           | Stylianos Basagiannis, Simone Fulvio Rollini (UTRCI)                                                                                             |  |

| v0.8    | 15.07.2025 | Liqun Chen (SURREY), Annika Wilde (RUB)                                                                                                                                                                                                                                                                       | Internal review                                                                                                                                  |  |

| v0.9    | 21.07.2025 | Refinements based on comments from internal review                                                                                                                                                                                                                                                            | Dimitris Karras, Thanasis Giannetsos (UBITECH)                                                                                                   |  |

| v1.0    |            | All results documented throughout the deliverable were ratified also against the end-to-end experiments performed in the context of the envisioned use cases (D6.2). This was the reason behind the consortium opting to submit the final version of all deliverables on M36 where all results were available | Dimitris Karras, Thanasis Giannetsos (UBITECH)                                                                                                   |  |

| v1.0    | 30/09/2025 | Submission of deliverable                                                                                                                                                                                                                                                                                     | Thanassis Charemis (UBITECH)                                                                                                                     |  |

REWIRE D3.3 Page 1 of 151

# **List of Abbreviations**

| Abbreviation                              | Translation                                    |  |  |

|-------------------------------------------|------------------------------------------------|--|--|

| ABE                                       | Attribute-Based Encryption                     |  |  |

| ABS                                       | Attribute-Based Access                         |  |  |

| ACC                                       | Assisted Cruise Control                        |  |  |

| AE                                        | Authenticated Encryption                       |  |  |

| AIC                                       | Attestation Integrity Verification             |  |  |

| AIK                                       | Attestation Identity Key                       |  |  |

| API                                       | Application Programming Interface              |  |  |

| ATL                                       | Actual Trust Level                             |  |  |

| BBL                                       | Berkeley Boot Loader                           |  |  |

| BIOS                                      | Basic Input/Output System                      |  |  |

| CDI                                       | Compound Device Identifier                     |  |  |

| CIV                                       | Configuration Integrity Verification           |  |  |

| CPU                                       | Central Processing Unit                        |  |  |

| CRL                                       | Certificate Revocation List                    |  |  |

| CRTM                                      | Core Root of Trust for Measurement             |  |  |

| DDA                                       | Direct Anonymous Attestation                   |  |  |

| DICE                                      | Device Identifier Composition Engine           |  |  |

| DID                                       | Decentralised Identity Documents               |  |  |

| DMA                                       | Direct Memory Access                           |  |  |

| EAP                                       | Enhanced Authentication Protocol               |  |  |

| ECU                                       | Electronic Control Units                       |  |  |

| EK                                        | Endorsement Key                                |  |  |

| EPC                                       | Enclave Page Cache                             |  |  |

| FPGA                                      | Field Programmable Gate Arrays                 |  |  |

| FSM                                       | Finite State Machine                           |  |  |

| HSM                                       | Hardware Security Module                       |  |  |

| HW                                        | Hardware                                       |  |  |

| IDM                                       | Identity Management                            |  |  |

| IOMMU Input/Output Memory Management Unit |                                                |  |  |

| ISA                                       | Instruction Set Architecture                   |  |  |

| ISO                                       | International Organization for Standardization |  |  |

| KMS                                       | Key management system                          |  |  |

| MUD Manufacturer Usage Description        |                                                |  |  |

| OEM                                       | Original Equipment Manufacturer                |  |  |

| PCR                                       | Platform Configuration Register                |  |  |

| PMP                                       | Physical Memory Protection                     |  |  |

| PPI                                       | Physical Presence Interface                    |  |  |

| PSK                                       | Pre-Shared Key                                 |  |  |

| PUF                                       | Physically Unclonable Function                 |  |  |

REWIRE D3.3 Page 2 of 151

| RA                                   | Rich Application                        |  |  |

|--------------------------------------|-----------------------------------------|--|--|

| RATS                                 | Remote ATtestation procedureS           |  |  |

| REE                                  | Rich Execution Environment              |  |  |

| RoT                                  | Root of Trust                           |  |  |

| RT                                   | Runtime                                 |  |  |

| SBI                                  | Supervisor Binary Interface             |  |  |

| SC                                   | Side-Channel                            |  |  |

| SDLC                                 | Software Development Lifecycle          |  |  |

| SGX                                  | Software Guard Extensions               |  |  |

| SM                                   | Security Monitor                        |  |  |

| SoC                                  | System-on-Chip                          |  |  |

| SP                                   | Service Provider                        |  |  |

| SRK                                  | Storage Root Key                        |  |  |

| SUIT                                 | Software Updates for Internet of Things |  |  |

| SSA                                  | Security-Sensitive Application          |  |  |

| SSI                                  | Self-Sovereign Identity                 |  |  |

| SW                                   | Software                                |  |  |

| TA                                   | Trusted Application                     |  |  |

| ТСВ                                  | Trusted Computing Base                  |  |  |

| TCG                                  | Trusted Computing Group                 |  |  |

| TDISP                                | TEE Device Interface Protocol           |  |  |

| TEE                                  | Trusted Execution Environment           |  |  |

| TMFS                                 | TEE Management Framework Specification  |  |  |

| TOCTOU                               | Time of Check Time of Use               |  |  |

| TPM                                  | Trusted Platform Module                 |  |  |

| TTP Trusted Third Parties            |                                         |  |  |

| UDS Unique Device Secret             |                                         |  |  |

| VC                                   | Verifiable Credentials                  |  |  |

| VM                                   | Virtual Machine                         |  |  |

| VP                                   | Verifiable Presentations                |  |  |

| vTPM Virtual Trusted Platform Module |                                         |  |  |

| ZTO                                  | Zero-touch onboarding                   |  |  |

REWIRE D3.3 Page 3 of 151

# **Chapter 1**

# Introduction

# 1.1 Scope and Purpose

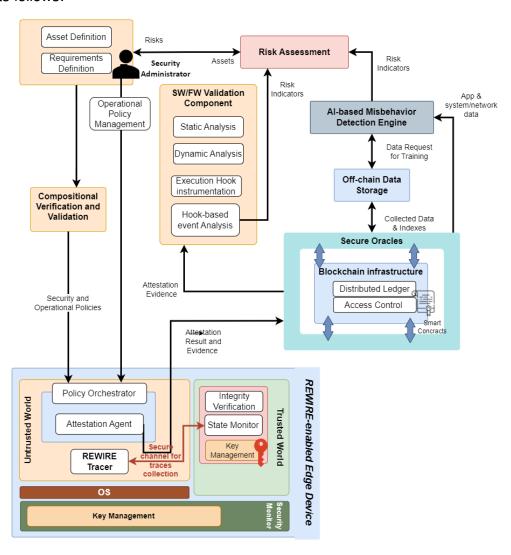

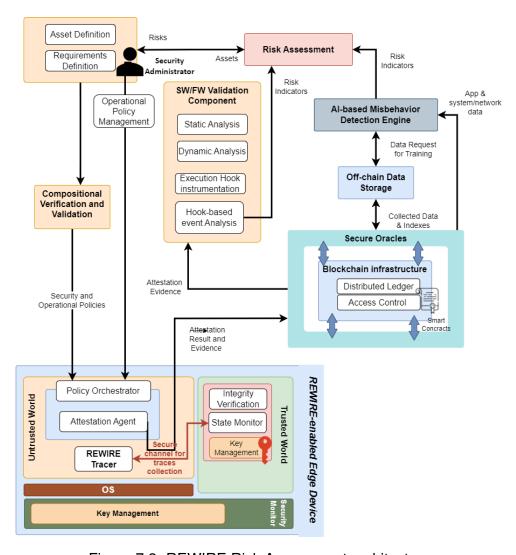

In order to achieve the core target of REWIRE pertaining to the secure lifecycle management of embedded systems considering the trend towards the increased adoption of OpenHW architectures through the provision of security and trust enablers, REWIRE provides a holistic framework, which aims to capture the entire operational lifecycle of devices operating in the context of large-scale **Systems-of-Systems (SoS)**. This framework aims to address the key challenge of ensuring the correctness of all software and hardware artefacts and achieve high security and trustworthiness profiles for embedded systems by providing a set of **security enablers and trust extensions**. In this regard, a core innovation of REWIRE is to support the **symbiosis of design-time with runtime assurances** as part of a **hybrid methodology**, by demonstrating how these enablers can work in order to fulfil the stringent **security and privacy requirements** characterizing such SoS.

As detailed in D2.2, the operation of the REWIRE framework can be split into two core phases, namely Design-time and Runtime. This deliverable is dedicated to the description of the final versions of all technical components participating in the Design-time phase of the REWIRE framework, which entails the instantiation of the REWIRE framework during the initial phase of its deployment, as well as the expression of the overarching requirements of the system, as provided by the Security Administrator, the Use Case Providers, and the OEM. The end goal of this phase is the definition of the trust boundary of the system, i.e., the set of device properties which can be formally verified during design-time, and for which the System Administrator can have the required guarantees on their correctness, through the Compositional Verification and Validation component (Chapter 3). Note that this component employs the **Verifpal** tool for Formal Verification, which provides the required level of abstraction for verifying the Elliptic-Curve Cryptography (ECC)-based Configuration Integrity Verification (CIV) scheme, which is a core innovation of REWIRE. In this regard, Verifpal has been identified as providing a high level of flexibility in capturing the underlying complex mathematical functions, compared to other existing Formal Verification solutions. Conversely, the parts of the system that remain outside the trust boundary cannot be formally verified during design-time, and need to be dynamically verified during runtime using the security enablers of REWIRE. To this end, a core output of the Design-time phase is the definition of security and operational policies that dictate the actions that need to be taken in order to verify that those runtime properties are correct, based on the expected behaviour of the device. Thus, the Runtime phase receives the outcomes of the Design-time phase, and prepares the device so that it can utilize the secure lifecycle management capabilities of REWIRE, and identify any unexpected behaviours so that the appropriate mitigation measures can be applied.

At the beginning of the Design-time phase, the **Service or Application Provider** and the **Security Administrator** provide information on the assets belonging to the target operational domain and their interconnectivity. In this regard, the **Risk Assessment** component of REWIRE (Chapter 7) is responsible for performing an initial **risk quantification** based on the most prominent types of threats and vulnerabili-

REWIRE D3.3 Page 4 of 151

ties affecting these devices, capturing all types of topologies and relationships between assets (SW-SW, HW-HW, and SW-HW relationships). Note that, in the context of REWIRE, we consider interactions and communication between both **devices belonging to the same service graph chain within a domain infrastructure**, or between **different domains**. Thus, REWIRE aims to provide the necessary cryptographic enablers for establishing secure and authenticated channels in both these types of scenarios (Chapter 8).

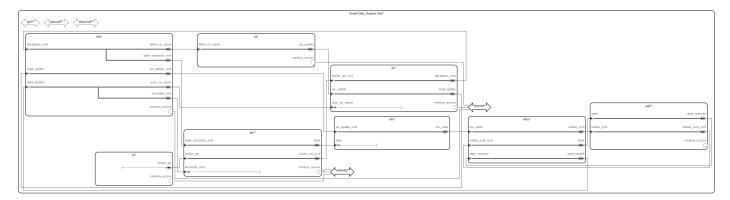

The REWIRE framework, as aforementioned, aims to provide operational assurance in large-scale SoS consisting of various interconnected devices. For the modelling and representation of such systems, REWIRE employs an **Architecture Analysis & Design Language (AADL)**-based methodology for specifying both SW and HW configurations. Specifically, REWIRE employs rigorous methodologies such as the **Open Source AADL Tool Environment (OSATE)**, which enables engineers to map cybersecurity requirements to system components. This approach assists in the identification of *requirements violations and security measures*, and ensures that each system component aligns with the overarching security goals of the target application domain. In addition, through the **RESOLUTE** extension, it is possible to build **assurance cases** (i.e., formal arguments linking high-level security objectives to evidence on the behaviour of low-level components) for validating and ratifying the achievement of the aforementioned requirements.

Another functionality provided by REWIRE for facilitating the software security analysis of large numbers of devices in such large-scale SoS is the SW/FW Vulnerability Analysis Component (Chapter 4), which enables the partial automation of the analysis of embedded software, through partial emulation of the firmware image and fuzzing of the emulation, where semi-random inputs are generated and mutated and the behaviour of the device is monitored. This process is also performed on any updates or patches to the firmware image of a device deployed through the Secure SW/FW Update process of REWIRE, which needs to be verified for any bugs or vulnerabilities. Note that the Secure SW/FW Update process of REWIRE, as analysed in Chapter 2, is supported by Authenticated Encryption (AE) capabilities for mitigating the threat of malicious software updates. Another core consideration of REWIRE in this regard is protection against Side-Channel Attacks (SCA), i.e., the exploitation of unintended information leakage from physical implementations, through the use of Ascon, which is a lightweight NIST-approved crypto schmeme designed for providing resilince against key leakage.

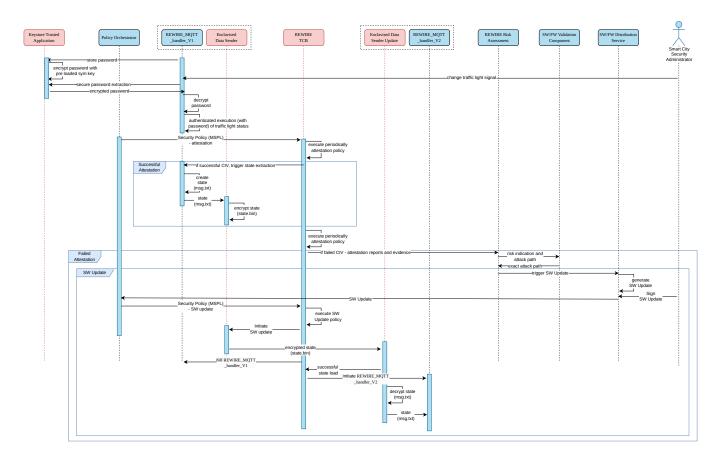

Finally, a core output of the Design-time Phase is the definition of actions that need to be taken during runtime for the verification of the correctness of the properties that need to be attested during runtime. This is achieved through the compilation of **security and operational policies** (Chapter 6), which are expressed using the **Medium Security Policy Language (MSPL)** which possesses the required level of expressiveness and granularity considering the security enablers offered by REWIRE. These are deployed through the **Policy Orchestrator**, which acts as a bridge between the device and the outside world, and distributed to the **Facility Layer** of the devices so that the necessary actions can be taken. In this deliverable, we provide concrete examples of such policies deployed in the context of the REWIRE framework for each of the three envisioned use cases (Smart Cities, Automotive, Smart Satellite).

Overall, this deliverable aims to provide a detailed description and documentation of all the components participating in the Design-time phase of the REWIRE framework and their demonstration through concrete examples and evaluation results. This provides the basis for the runtime operation of the REWIRE framework, through the provision of all required information to guide the **trust assessment** of the devices. Note that, while the provision of a Trust Assessment Framework falls outside the scope of REWIRE, we aim to provide all tools and functionalities that enable calculating both the **Required Trust Level (RTL)** and the **Actual Trust Level (ATL)** of the devices, and ensuring the trustworthiness level of the devices through the available security enablers.

REWIRE D3.3 Page 5 of 151

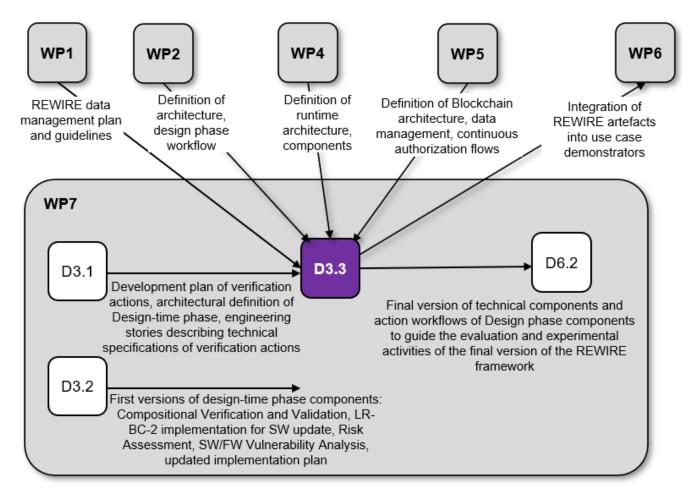

Figure 1.1: Relation of D3.3 with other WPs and Deliverables

### 1.2 Relation to other WPs and Deliverables

Figure 1.1 depicts the relationships of this deliverable with other Work Packages (WPs), as well as other tasks in the same WP(3). As aforementioned, the main purpose of this deliverable is to provide a detailed description and documentation of all technical components participating in the Design-time phase of the REWIRE architecture, as well as their role within the overall REWIRE workflow. Thus, this deliverable receives input from D3.1 with regards to the development plan, the architectural definition of the Design-time phase, and the engineering stories involving the concerned technical components, as well as D3.2 regarding the initial definitions of all technical components to be expanded upon in this deliverable.

In addition, D3.3 receives input from the reference architecture of REWIRE defined in the context of WP2, and specifically D2.2 which defines the final action workflow of the Design-time phase of the REWIRE framework. These also provide the basis for the operation of the components defined in the context of WP4 regarding the runtime operation of the REWIRE framework, as well as the Blockchain infrastructure defined as part of WP5. Finally, D3.3 provides input to WP6, which is responsible for the integration of all REWIRE components into the overall framework, as well as the experimental activities for the evaluation of the performance of all technical components as part of the envisioned use cases of REWIRE.

### 1.3 Deliverable Structure

This deliverable is structured as follows:

Chapter 2 is dedicated to the description of the Secure SW Update process with Authenticated Encryption (AE), including the design of a masked gadget against physical faults, and evaluation of primitive-

REWIRE D3.3 Page 6 of 151

and model-level countermeasures.

**Chapter 3** describes the Compositional Verification and Validation Component of REWIRE, as well as the formal verification of the Configuration Integrity Verification (CIV) process of REWIRE with local attestation.

**Chapter 4** describes the SW/FW Vulnerability Analysis component, the updates performed to the Qiling framework, and benchmarking results on the component.

**Chapter 5** is focused on the Architecture Analysis & Design Language (AADL)-based System Modelling methodology of REWIRE for specifying software and hardware configuration, as well as its use for the traceability of the achievement of requirements of the technical components of REWIRE.

**Chapter 6** describes the definition of REWIRE policies expressed in the Medium Security Policy Language (MSPL), and provides examples in the context of all envisioned REWIRE use cases.

**Chapter 7** describes the Risk Assessment component of REWIRE, with particular focus on the instantiation in the Automotive use case, as well as the process for the calculation of the Required Trust Level (RTL) of the device.

**Chapter 8** describes the process for the establishment of secure authenticated channels in the context of REWIRE, inspired by the Anonymous Authenticated Credential Key Agreement (AACKA) and leveraging BBS signatures.

Chapter 9 concludes the deliverable.

REWIRE D3.3 Page 7 of 151

# **Chapter 2**

# REWIRE Secure SW Update Process with Authenticated Encryption

In the type of modern large-scale Systems-of-Systems (SoS) and IoT environments considered in the context of REWIRE, enhancing the recovery and resilience of systems through software and firmware updates is becoming increasingly crucial, as threats of attackers aiming to substitute legitimate software and firmware with their malicious code are becoming increasingly prevalent in such ecosystems. Thus, *it cannot be assumed that the software and firmware of embedded systems will remain uncompromised.* To this end, the **Secure SW/FW Update process with Authenticated Encryption (AE)** of REWIRE aims to provide a mitigation strategy against such types of attacks. Note that, as outlined in D3.2, REWIRE offers two modalities for the SW Update process, specifically:

- "1-to-1" for the distribution of an update to a single device. In this case, as described in D3.2, the SW Service Provider signs and encrypts the update using an authenticated encryption (AE) algorithm, using a pre-established LRBC Key which is stored in the ASIC-based HW of the device. This has been implemented in the form of an enclave in order to ensure the protection of the key.

- "1-to-many" for the distribution of an update from a single source to multiple recipients. In this case, the SW Service Provider signs the update with their own key, and all concerned devices are notified about the update through the Blockchain Infrastructure.

In both cases, a Configuration Integrity Verification (CIV) process (i.e., the attestation enabler for verifying the correctness of the device configuration based on its expected state) is performed both before the installation of the update in order to verify that there are no integrity issues prior to its deployment, and after the update in order to verify that the update has been performed correctly. In the latter case, attestation reports are created for each device an update has been performed on. Then, an attestation report is created, authenticated, and encrypted with the LRBC Key, so that the SW Service Provider can verify the correctness of the update (and that the update has been installed on the intended devices, in the "1-to-many" case). Throughout this chapter, we provide a detailed description of the SW Update Process of REWIRE, where AE is used for ensuring the secure communication of SW updates, while ensuring the protection of the process against the types of attacks that may target the update process, as aforementioned.

As outlined in D3.2, the aim of REWIRE is to offer a general framework, following the relevant best practices, that is able to ensure the fulfilment of the needs and requirements of each target embedded system and environment. To this end, **REWIRE is aligned and shares a common vision with the Trusted Computing Group (TCG)** with regards to the best practices regarding the secure software and firmware updates of embedded systems [72]. Based on the guidance provided by the TCG, a set of requirements have been identified with regards to the design and implementation of a SW/FW Update system for securing the lifecycle management of the aforementioned types of environments. Here, we provide a summary of these requirements, as well as the actions taken by REWIRE for their fulfilment:

REWIRE D3.3 Page 8 of 151

- Secure Development: This refers to the need to conduct a comprehensive threat analysis during the design phase of a system, in order to ensure that the available security measures are able to address the evolving threat landscape affecting the system. According to the TCG, additional practices for higher security levels are required, including automated testing (e.g., fuzzing) for the identification of bugs or security vulnerabilities, and static analysis of binary or source code to identify bugs or poor coding practices. This has been integrated into the Design-time Phase of REWIRE, where system designers and security analysts define the properties that need to be validated for fulfilling the overarching requirements. In addition, the SW/FW Validation Component of REWIRE is responsible for performing the aforementioned automated testing and static analysis.

- Secure Update Signing: This refers to the need to sign a software update in order to verify its origin and integrity before sending it, with a process referred to as code signing. The code signing process has been notably targeted by malicious parties, using attacks that aim to distribute malicious code with a valid signature, either by exploiting flaws in the validation of the signature, or by obtaining the actual signing key, resulting in the distribution of malicious code without being noticed. To this end, the TCG proposes methods such as the use of reliable, well-vetted cryptographic algorithms and tools, the use of cryptographic algorithms with high agility, and the use of Hardware Security Modules (HSMs) for cryptographic key management. These are all offered in the context of REWIRE, as well as enhancements such as the use of TEEs for performing isolated and secure execution of the signature validation, and rollback protection.

- · Robust Distribution and Authentication: After a SW update has been signed, it needs to be distributed to the intended devices, even in cases where the distribution of large files to numerous devices in a scalable manner is needed, or in cases where the distribution network is sporadic and may lead to fragmented data transmissions. In fact, the latter is a core concern for the Smart Satellites use case of REWIRE, where satellites in orbit receives update in data chunks based on the visibility they have with ground stations while moving around the Earth. In this regard, the TCG recommends a set of best practices, including securing communications with thoroughly vetted security protocols, establishing the identity and trustworthiness of the distribution service, designing SW update distribution mechanisms in a manner that avoids overloading networks or servers, placing the communication security keys in an HSM, authenticating endoints to determine which updates they are authorised to receive, tracking installation of updates to ensure that endpoints have been updated, and alerting administrators if updates cannot be installed on some endpoints. REWIRE offers all aforementioned measures, and applies Formal Verification methods in order to guarantee the correctness of the LR-BC-2 AE scheme, which is used in order to secure the communication channel for the distribution of SW updates. The use of this scheme ensures authenticity, thus ensuring that the identity of the distribution service is correct, in both modes of operation ("1-to-1" and "1-to-many"). In addition, the Automotive use case of REWIRE also requires confidentiality against external observers, which is provided by the AE used in the "1-to-1" scenario. Finally, REWIRE enables devices to transmit the outcome of the update process in an authenticated manner using AE.